초음파를 이용한 거리측정 회로 분석 및 설계

사용 툴 : OrCAD PSpice

사용 장비 : Oscilloscope, Multimeter

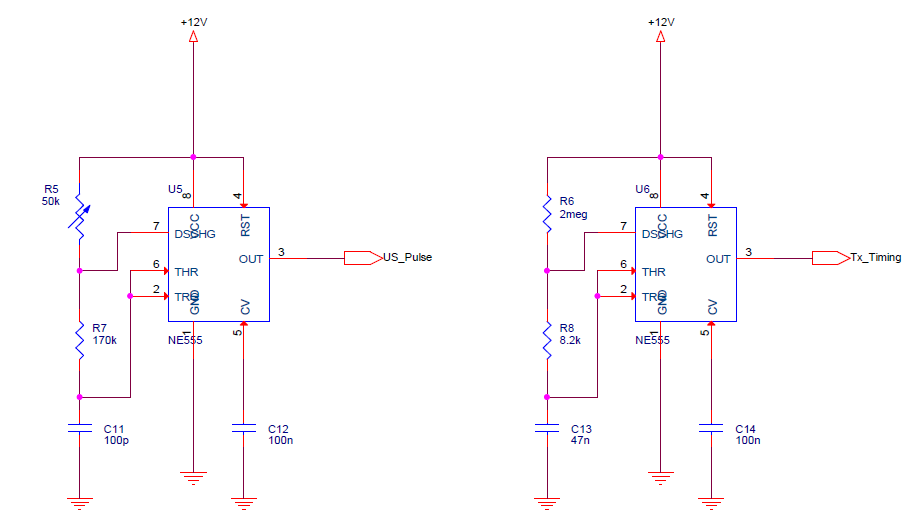

1. SE-400ST160(초음파 송신기)의

초음파 최대 파워 출력 조건 40kHz 이므로

공진 주파수를 맞추기 위해

발진기의 목표 주파수는 40kHz

2. NE555의 주파수 공식

f = 1/0.69(R_A+〖2R〗_B )C[HZ] 를 이용해

적당한 저항 값(Ra, Rb)과

커패시터 값(C) 설정

송신부는 초음파를 조금이라도 세게 보내기 위해

1. 입력 전류 I_i 출력 전류 I_o가 있을 때

Gain(I_o/I_i ) > 1의 특성을 가지는

Not Gate(Inverter)를 사용하여 전류(I) 증폭

2. B Node에 커패시터를 연결하여

들어오는 dc를 없애고 ac만 살리면서

+12V ~ 0V(12V) 파형을 0V ~ -12V 파형으로 변형

송신부로 -12V ~ +12V 전압(24V) 인가

=> Voltage Doubling으로 전압(V) 증폭

수신부는 들어오는 아날로그 신호가 매우 약하기 때문에 RC4558 OP-Amp를 사용해서 100배 증폭을 목표

1. RC4558을 되먹임(Feedback) 없이 썼을 때 Open Loop Gain(증폭도)은 약 10000배(∞)

필요한 100배 정도의 증폭을 얻기 위해 출력 값을 – 단자로 되먹이는 Negative Feedback 사용

2. Negative Feedback을 사용하는 경우, 공식 V_o (출력전압) = A(Gain) * 〖(V〗_+ – V_-)에 따라

=> V_+ – V_- = V_o/"A" (= 0)(V_o 는 〖V_EE ~ V〗_CC 의 유한한 값, A는 약 10000배(∞)이므로)

=> V_+ = V_- = Virtual Short = +단자 전압과 –단자 전압과 같음

그러나 실제로는 V_in 의 영향을 받아 –단자 전압이 달라짐

그것을 방지하기 위해 De-Cap C 추가

3. OP-Amp의 -단자의 저항은 ∞이므로

R_i 와 R_f는 직렬로 연결되어 있어

흐르는 전류가 같음

=> (V_i " - 0" )/R_i = ("0" - V_o)/R_f

=> V_o = - R_f/R_i 공식에 의해서

R_i 와 R_f의 비율을 조절하여 증폭비율 조정

※OP-Amp 증폭 최대 범위는 V_CC 와 V_EE사이

12V Power Supply와-12V Power Supply를 다 쓰게 되면

부피, 가격 손해 => Single Bias로 변경

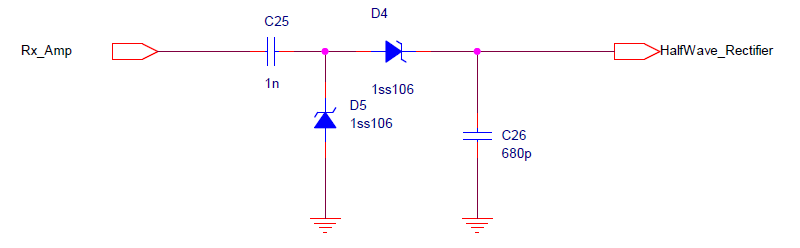

증폭된 아날로그 신호에

반파정류회로와 평활 커패시터 C를 통과하게 해서

-전압을 없애고 파형을 직류(DC)에 가깝게 만듦

※SBD1의 존재 이유는 SBD2가 충방전 될 때 –전하를 충전하여 충방전이 늦어지는 것을 방지하기 위함

※증폭되어온 신호가 1V로 매우 낮은 신호가 오기 때문에

Forward Voltage가 낮은 SBD를 사용해야 신호가 잘 전달 되어짐

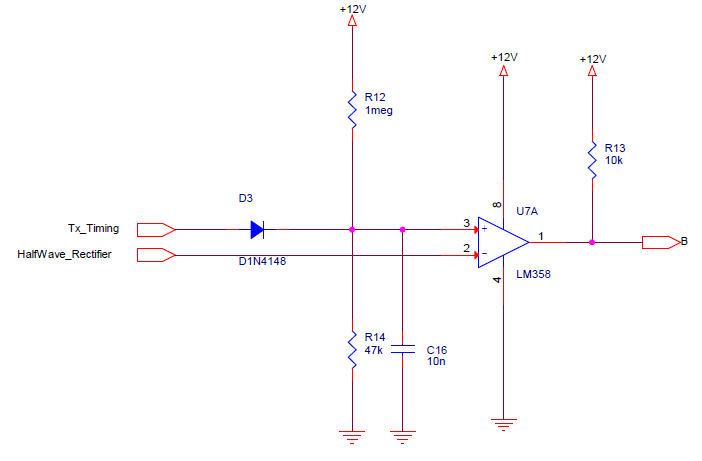

1. 송신부에서 초음파를 보냈을 때

회절 현상으로 옆에 있는

수신부가 바로 수신할 수 있는 문제

이 것을 해결하기 위해

15Hz 발진기 펄스를 +단자로 입력

2. 검파회로의 출력을 –단자로 입력

비교기의 기능 V_o = A(V_+ - V_-)

V_+ > V_- 일 때 V_o = ∞ * 양수 = V_CC = H

V_+ <〖 V〗_- 일 때 V_o = ∞ * 음수 = V_EE = L

A Node에 약 0.5V 문턱 전압을 걸어두어 V_- 에서 들어오는 공기 중 Noise를 차단

15Hz 발진기에서 펄스 나오면(초음파 송신하면)

A Node에는 11.3V가 걸리고 출력 B는 무조건 High

즉, 송신 시작 후 일정 시간 동안은 수신된 신호 무시

※비교기(Comparator) 대신 빠르게 동작할 필요 없는 이 시스템에서 안정성을 높이기 위해

동작이 비교적 느린 OP-Amp를 비교기로 사용

15Hz 발진기 펄스 A가 들어오면 High

수신 펄스 B가 들어오면 Low

송신 타이밍, 수신 타이밍을 알려주는 역할

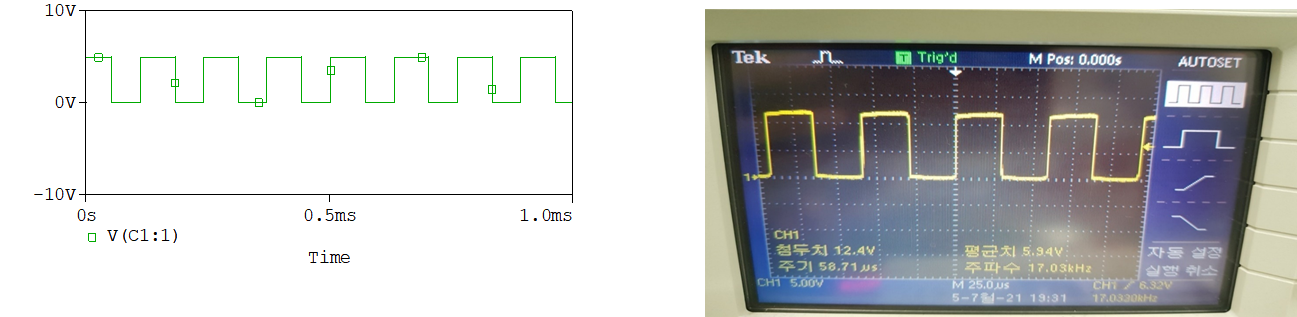

CMOS Inverer를 사용한 발진회로

1. 측정 최대 거리 1M로 설계

음파속도 약 340m/s

거리가 1M 일 때 걸리는 시간

= 왕복 2[M] / 340[m/s]

= 5.82ms = 171.8Hz

1M 일 때 100펄스로 설계

171.8 * 100 = 17.18kHz

2. C8에 4.7n를 배치하면

17.18kHz = 1/(2.2 ∗ R3 ∗ 4.7 ∗〖 10〗^(-3) )

R3은 10k

주파수 세부 조절은 R3 조정

R3을 올릴 수록 주파수 ↓

R3을 내릴 수록 주파수 ↑

주파수 공식

f = 1/(2.2 ∗R3 ∗ C8)[Hz]

1. R1 Pull-up Resistor로 12V 상태

Rx에서 들어오는 송수신 타이밍 파형을

C에 의해 Rising Edge, Falling Edge만 통과

D1에 의해 High 신호는 12.7V로 고정

2. R2 Pull-down Resistor로 0V 상태

Rx에서 들어오는 송수신 타이밍 파형을

C에 의해 Rising Edge, Falling Edge만 통과

D2에 의해 Low 신호는 -0.7V로 고정

3. NOT Gate의 Gain > 1 특성을 통해 전압 일정하게 정리

4553 내부에 있는 스캔 발진기 주파수로 FND를 선택

스캔 발진기의 주파수는 C의 값으로 조절

전압은 12V, C 값은 약 1n(공식 단위는 uF)

5 / 0.001 = 5kHz

이 주파수를 통해 발진기는 FND에 1초에 약 5000번 번갈아 전원을 공급한다

1. 초음파를 송신하면 RST으로 Falling Edge가 들어오며 카운터 초기화

2. CLK로 최대 거리인 1M일 때 100번 카운트하는 17.18Hz의 클럭이 카운터를 동작

3. 초음파가 수신되면 LE로 Rising Edge가 들어오며 카운터 값 Latch로 저장

※Latch에 데이터가 저장되면 다음 수신 시점인 65ms 뒤 이므로 1초에 약 15번 표시 가능

기존 회로 문제점 및 개선사항

회로에 아날로그 신호 처리 부분이 있어 노이즈에 민감한 아날로그 회로 불안정성

아날로그 VCC에 Beads, Capacitor 병렬 배치하여 다른 IC에서 전류를 사용할 때 생기는 노이즈 차단

커패시터 값은 매우 작은 크기와 비교적 큰 크기의 값을 그래프를 비교한 뒤 범위를 줄여가며 선택

Beads는 Laird 사의 MI0603J601R-10 사용, 선택 이유는 회로의 전류가 1A를 안넘기 때문에

아날로그 GND에 Beads 배치

RC4558 OP-Amp의 Unity Gain Frequency(UGB)는 3MHz이고

UGB = Gain * BandWidth 공식에 의해 40kHz 대역에서는 최대 Gain이 약 75배

목표 주파수 범위인 40kHz 대역에서 100배 증폭하기 위해 10배를 2Stage 형태로 100배를 만듦

(Gain)Av = - Rf / Ri = 100k / 10k = 10배

FND COM 단자의 스위치 역할을 하는 BJT(PNP TR)의 Parasitic Capacitor가 존재하여On/Off 될 때 전류가 급격히 변해 BJT의 수명이 짧아짐

Base Resistor를 넣어 전류를 감소시켜 Parasitic Capacitor의 충방전 속도 감소(안정성 증가)

Base Resistor의 값은 소신호 기준 들어오는 전류 I_B 를 250uA로 가정하여

I_B = (V_CC - 0.7) / R_B => 250u = (12 – 0.7) / R_B => 250u = 12 / R_B

R_B = 12 / 250u => R_B = 48k => 저항 표준 값 중 비슷한 47k 사용

정전기 방전(ESD) 대책이 없어서 회로가 손상될 수 있음

VCC 앞에 Varistor를 배치

선택 이유 : 파워 관련이라 고속신호가 아니기 때문에

Varistor는 TDK 사의 AVR-M1005C270MTAAB 선택

선택 이유 : 12V 전압원을 사용하기 때문에 정격전압이 1.3배 높은 15V 짜리 사용

PCB 기판에 GND가 도포되어 있지 않아 열 발산, 노이즈, EMI 개선이 안됨

PCB 제작 과정에서 Copper Pour 추가

Clock 선이 길어 ESL이 증가

Clock Line 짧게 부품 배치 및 배선

동작 영상 링크 : https://www.youtube.com/watch?v=gli5xxqdkvg